复杂大规模数字芯片设计,芯动科技IP和思尔芯EDA带来简单“解题思路”

-

正文

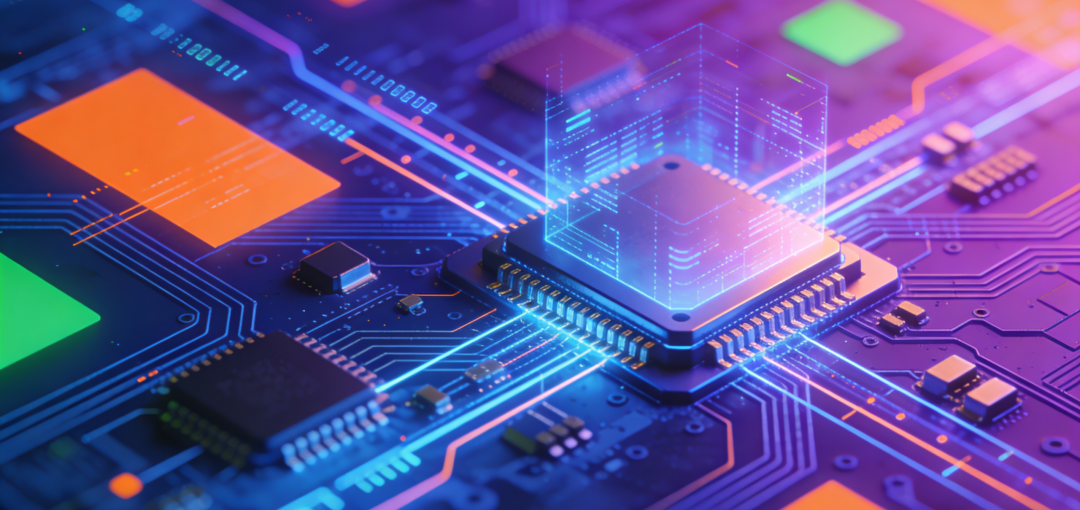

又到岁末年初时,回顾2023年,AIGC技术、Chiplet、RISC-V以及新能源汽车当仁不让是行业热词。尤其Chiplet技术,被视为是摩尔定律延续的新解,将会持续推动大规模数字芯片的PPA提升,进而为AIGC、AI PC、ADAS等应用提供更高算力支持。

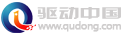

时间来到2024年,Chiplet劲头不减。MIT科技评论将其列为2024年的十大突破性技术之一;中国新推出的《芯粒间互联通信协议》标准从1月1日起开始实施;Intel在近日CES上也推出了其第一个Chiplet汽车SoC平台,将AI PC带入到了智能汽车中。

然而像采用Chiplet技术的这种高性能计算芯片,对于整个芯片设计流程提出了全新的考验。传统的EDA工具和设计范式已经不足以应对当下的芯片设计工作,IP与EDA的生态系统的融合,正为我们开辟一条新的敏捷设计之路。

图:MIT科技评论2024年十大突破性技术

为什么大规模芯片设计越来越难了?

如果把造芯片比作造房子,那么IP类似于预制的建筑组件,可直接集成到电路中,节省设计时间并降低错误风险。“IP其实就是传统意义上的一块芯片的可复用的功能实现,某种意义上它还是数字化验证过程中的一个中间件,客户可以在EDA工具中提前完成系统验证。”芯动科技董事长兼CEO敖海如是说到。“EDA工具加IP组件能够实现用户在中间设计过程中的自由组合,实现工具的流程化、验证的自动化和设计的自动化。”

而EDA工具就像建筑师的设计工具,帮助其设计电路图,进行模拟测试,确保电路的性能和可靠性,同时优化成本和功耗。“好的工具的角色就是把芯片设计变成自动化,最主要的是怎样缩短整个设计周期的时间,同时还能开发出具有更高效能、更低功耗以及更有竞争力的芯片。”思尔芯董事长兼CEO林俊雄解释道。

随着工艺制程发展,数字芯片的规模越来越大,从最初几十个晶体管到现在动辄上百亿的晶体管;同时,伴随着新兴应用场景的演进,对于数字芯片也提出了更高的要求。例如,AI应用需要强大的并行处理能力和极低的延迟;汽车应用追求低延迟和高可靠性;而IoT应用强调低功耗和低成本。这一系列的需求使得芯片设计更加复杂,催生出了新的技术和创新设计方法。

Chiplet技术通过模块化方式组合不同功能芯粒,大大提高了数字芯片的集成度和性能,但也带来新的挑战,如IP融合、高速互连、热管理、应力分布和高频信号完整性等。

现在,开发大规模数字芯片需要巨大的前期投资,包括研发和制造成本,给许多公司带来财务负担。在快速发展的市场中,维持竞争优势需要不断推出新技术和更新产品,这也进一步增加了芯片设计难度和竞争压力。

面对这些挑战,芯片设计企业发现依靠单一的EDA或IP供应商难以应对市场变化和技术发展。他们需要的是能够提供全面解决方案的生态系统,以支持复杂设计和快速开发周期。芯动科技和思尔芯的合作,通过在各自领域的优势互补,简化了芯片设计,为客户实现了敏捷高效和可靠的开发体验。

IP+EDA,加速大规模数字芯片设计

随着技术的发展和市场竞争的加剧,对快速、高效的电路设计需求日益增长,IP厂商和EDA厂商和之间的合作应运而生。双方通过整合资源、发挥各自技术专长,使得IP核心可以更加顺利地融入到复杂的电路设计中。这种合作显著提高了芯片设计流程的效率,减少了从概念到最终流片的时间,并提高了最终芯片的质量和性能。设计工程师现在可以将更多的精力投入到创新和优化上,而不是在复杂的基础设计上耗费时间。

据林俊雄介绍,思尔芯和芯动科技在芯片设计领域开展的合作可以分为三个层面。

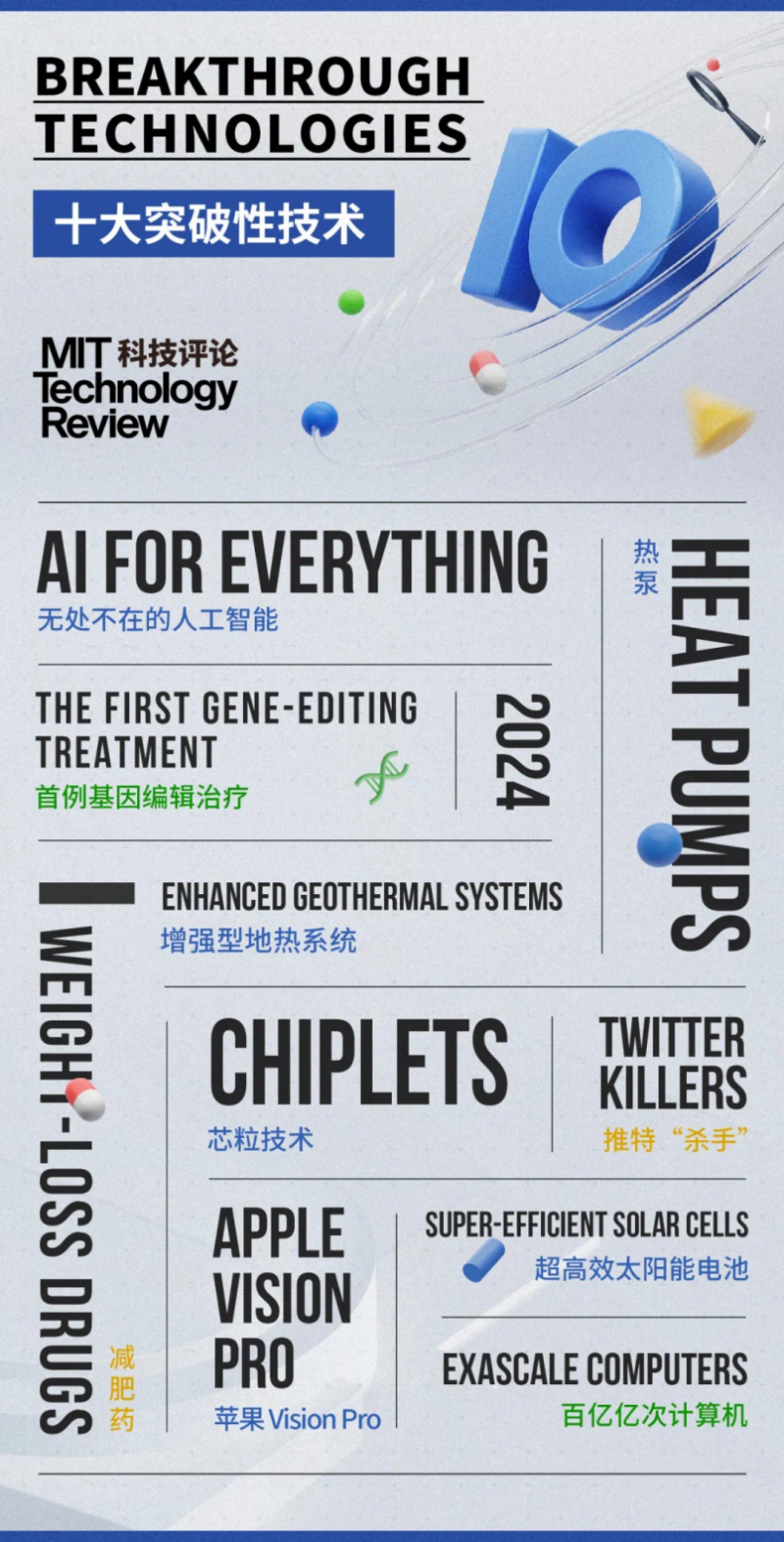

首先是在单个IP层面,完善了验证和接入工作。芯动科技的各种接口IP绝大部分都已经在思尔芯的EDA工具上完成了验证,并且在思尔芯原型验证系统上提供了参考设计。因此客户在选择了芯动科技的IP之后,不需要从零开始学习这一IP的使用,只需关注如何将其与自己的现有设计进行整合即可。对于已经在思尔芯的芯神瞳原型验证系统上进行验证的客户而言,当整合芯动科技IP的时候,整个设计的衔接会非常快。

其次是在SoC层面,针对汽车、物联网、AI计算等多个热门领域,双方提供了完整的SoC平台。例如在IoT方面,客户可以在既有SoC平台基础上,结合其实际应用场景需求,在验证工具和芯神瞳原型验证上裁剪掉多余的功能,或者新增自己需要的功能,然后进行重新设计。

在选定的特定领域的SoC平台上,客户可以在很短时间内完成一个贴近自己具体应用需求的SoC重建,利用原来SoC平台已有的验证架构,客户可以对自己新构建的SoC设计进行充分验证,加速软件开发进程,提前实现系统的整合。

最后是在设计更前端的层面,提供系统级解决方案。当下流行的大规模数字芯片设计复杂度极高,需要提前进行微架构的探索与观察;像Chiplet一类的芯片,要求在整个设计的更早阶段就进行系统架构评估,客户通常需要在RTL设计之前,甚至在选择IP时,就完成大量的系统性能评估。

思尔芯公司已经将芯动科技的许多IP和模块整合进了其系统架构工具中,这使得客户能在早期阶段就预判如何构建他们的SoC,决定需要哪些类型的IP。此外,该平台还能与思尔芯的其他软件仿真和硬件仿真工具实现无缝整合。“

也就是说,在设计过程中,客户可以在架构设计伊始,从很高层次的模型一步一步移植到软件仿真、硬件仿真,最后移植到原型验证中,在还没投片之前完成整套系统级的设计。”林俊雄解释道。

图:思尔芯芯神瞳原型验证解决方案

除了上述提到的三个层面的优势外,选择芯动和思尔芯的方案,还让客户能够站在双方几十年的知识积累和客户经验上,避免踩坑的同时实现更逼近真实的仿真验证。

在芯片设计阶段进行IP选择时,一家专注于自动驾驶SoC的公司就遇到了挑战。他们在物理接口(PHY)和控制器(controller)部分遇到了若干兼容性问题,这些问题长期困扰着他们。通过对多种解决方案进行对比择优,他们最终选择了芯动科技和思尔芯的IP+EDA敏捷开发平台。

基于这一平台,客户无需自行处理IP适配和设计验证问题,可以直接采用在现场可编程门阵列(FPGA)平台上验证过的参考设计,并将其应用于他们整体的SoC环境。这种方法大幅节省了设计所需的时间和精力,对客户而言至关重要。

如果他们无法解决这些兼容性问题,他们甚至将无法预知何时能完成芯片的流片(tape out)。由此可见,芯动科技和思尔芯的此次强强联手,在帮助客户解决关键技术难题方面起到了重要作用。

近日,思尔芯也迎来了创立二十周年的重要时刻,在全球服务了包括英特尔、瑞昱、黑芝麻智能、开芯院等在内的累计600余家客户,其中包含世界前十大半导体企业中的六家、中国前十大集成电路设计企业中的七家。

芯动科技在其十八年的历程中,也已经实现了200多次成功流片和100亿颗高端SoC的量产出货。在先进工艺上,也一直与台积电、三星、中芯国际、格芯、联华电子、英特尔、华力等保持密切合作,在Chiplet、HBM3E、GDDR6X/6、PCIe5等大规模芯片必备的高带宽技术上保持领先优势。

据敖海分享,随着芯片尺寸越来越大,功能越来越多,接口越来越丰富,其中也存在越来越多的IP互连挑战。而芯动科技和思尔芯双方在服务了大量相同的客户中,已经积累了大量该方面的知识,因此可以帮助后面的客户避免很多的“坑”。

而站在这样的领先客户设计的基础上,也就让敏捷开发平台具备了非常强的逼真度。此外,芯动科技把服务其他客户的经验,应用于新客户的IP集成和芯片定制全流程中,缩短了系统验证周期。

“芯动科技和思尔芯在系统搭配这个过程中形成一种互相支持的体系,使我们的交流和客户沟通的窗口变得更加的容易。”敖海说道,“芯动科技会把IP处理器和相关系统复杂程度的知识,教会给某些不熟悉这些领域的客户,并且把原型验证系统作为软硬核IP的模式呈现给他们。”

从小积木到大积木,让Chiplet系统级设计仿真更轻松

随着晶体管工艺达到物理极限,要延续芯片在摩尔定律上的PPA提升,业界将会加速转向Chiplet技术生态。同时对于国内芯片产业而言,在先进制程受限的情况下就必须在成熟工艺上追求芯片性能突破,也必须要走Chiplet之路,进行成熟工艺的组合。

但使用Chiplet来进行芯片设计,整个芯片的规模会进一步加大,其中的IP和Die的组合也会越来越复杂,也就带来了更多种软硬件组合的可能。这也意味着很多系统级的考量——包括封装、后端设计到物理实现等,都要在芯片设计的很早期就要去完成。

林俊雄举例,如果说EDA+IP是使用了更大积木来搭建房子,那么Chiplet就是用超大的积木来搭建房子。而在使用超大积木(Chiplet)进行设计的过程中,思尔芯和芯动科技的EDA+IP这套体系的优势会进一步扩大。

敖海表示,使用Chiplet进行芯片设计,带来了更多的“大积木”的组合方式,而芯动科技和思尔芯的合作,可以帮助客户从系统架构和硬件评估的角度,把Chiplet的组合提前适配好。

在兼容性方面,芯动科技是最早支持UCIe并完成适配的IP厂商,并且提供了非常好的性能功耗表现。早在该协议公布两年前,芯动科技就和英特尔进行了合作开发。据悉,芯动科技的接口IP可采用DDR的模式操作Chiplet,这种端到端连线可以直接通过GPIO在原型验证上进行互连,客户只需要调整频率就可以完成整个Chiplet在延迟总线、整体协议方面的全套仿真和验证工作,而且兼具密度高、低延迟,PPA优势大幅提升。

目前,芯动科技的Chiplet硬化模块已经在思尔芯的原型验证中成功实施,通过FPGA与FPGA互连就能够完整地仿真整个Chiplet的总线功能。此外,客户还可以通过芯动科技的Chiplet PHY芯片,在两套原型验证之间实现高速模式或低速模式的互连。

图:芯动科技Chiplet产品组合

“在Chiplet领域,我们不但提供多种互联方式,也给客户提供大量互联的可定制化协议能力,并且已有很多成功经验能帮助到大家把芯片组合的风险降到最低。”敖海进一步分享到,“在GPU/AI等大型芯片中可能涉及到很多内核之间的数据交换,在这一过程中任何卡顿或协议问题都将会影响整体芯片的性能评估。光通过仿真几天几夜也仿真不出来,甚至一个月也仿真不出来,而通过敏捷开发验证平台,就可以快速实现这一步跨越。可组合的Chiplet加上可组合的平台,就能给客户提供大量敏捷开发的能力,以及来自思尔芯和芯动科技的专业知识深度。”

随着Chiplet的未来发展,思尔芯灵活的大型原型验证和芯动科技多种Chiplet模块相组合绑定,将会是一种市场趋势,也会为双方带来极大的优势。对于客户的设计而言,在追求Chiplet更好模式和仿真结果的过程中,也会变得更容易达成。

结语

随着边缘计算、人工智能、ChatGPT等大模型语言(LLM)的发展,对于芯片算力需求会呈几何级数增长。未来2~3年,将会是从端到云到车遍地开花的芯片时节。

而中国是实施最贴近应用端的市场,也是最需要多元化、快速迭代的市场,这将会成为高端芯片孵化培育的沃土。把握住这一波浪潮,中国半导体产业便有望在国际舞台上再上一个台阶。

双方一致认为,IP+EDA本身其实还有很多关键技术,整个产业链也需要更多合作伙伴包括学校和政府等一起协助来完成。国内需要创建这样一个共赢的生态,走出中国特色的半导体产业。

评论 {{userinfo.comments}}

-

{{child.nickname}}

{{child.create_time}}{{child.content}}

{{question.question}}

提交

一加 15T 售价 4299 元起,性能续航超越大屏,旗舰体验完胜小屏

vivo蓝图影像专业再突进,新一代“专业V单”装进完整创作系统

无感折痕,久用平整,全新OPPO Find N6开启折叠屏无感折痕新世代

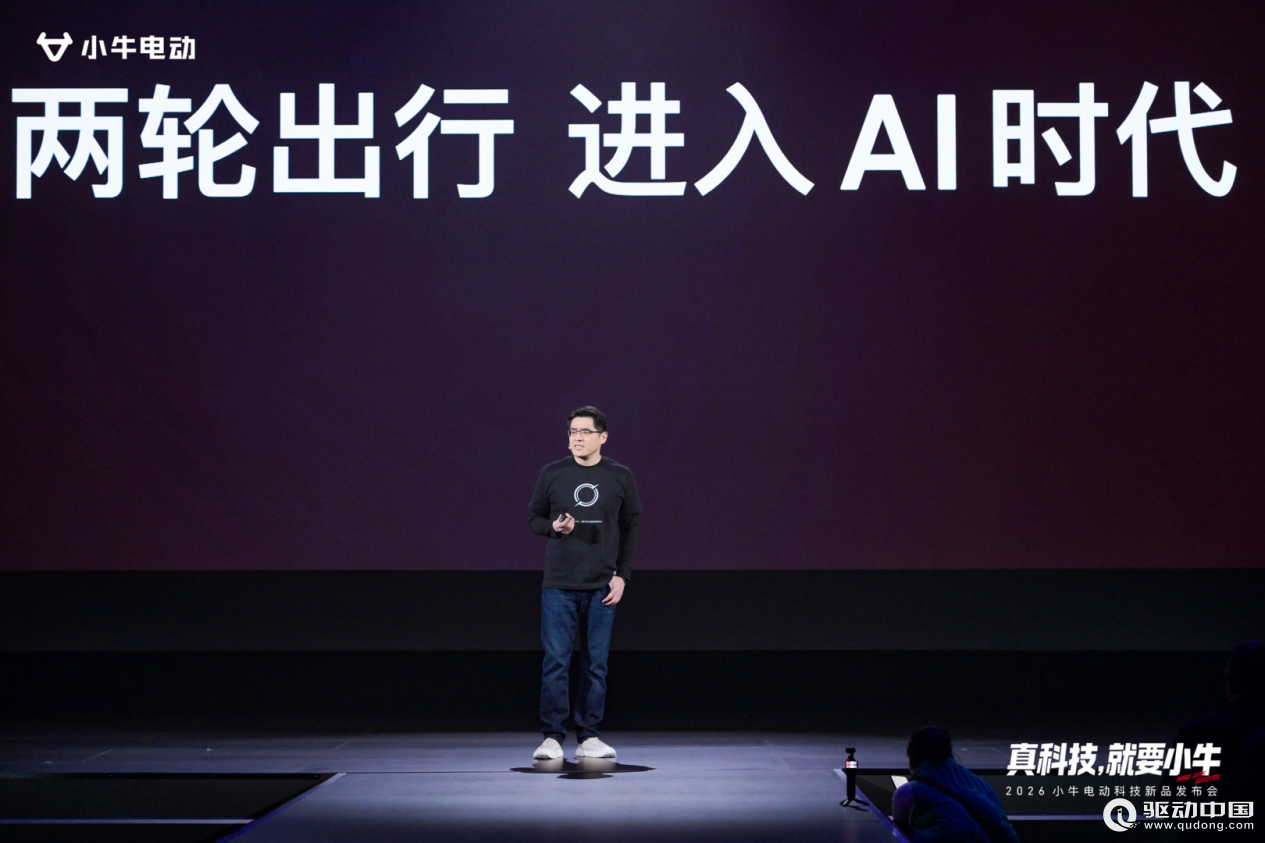

小牛电动举办2026科技新品发布会,开启“造AI好车”新十年

驱动号 更多