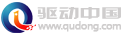

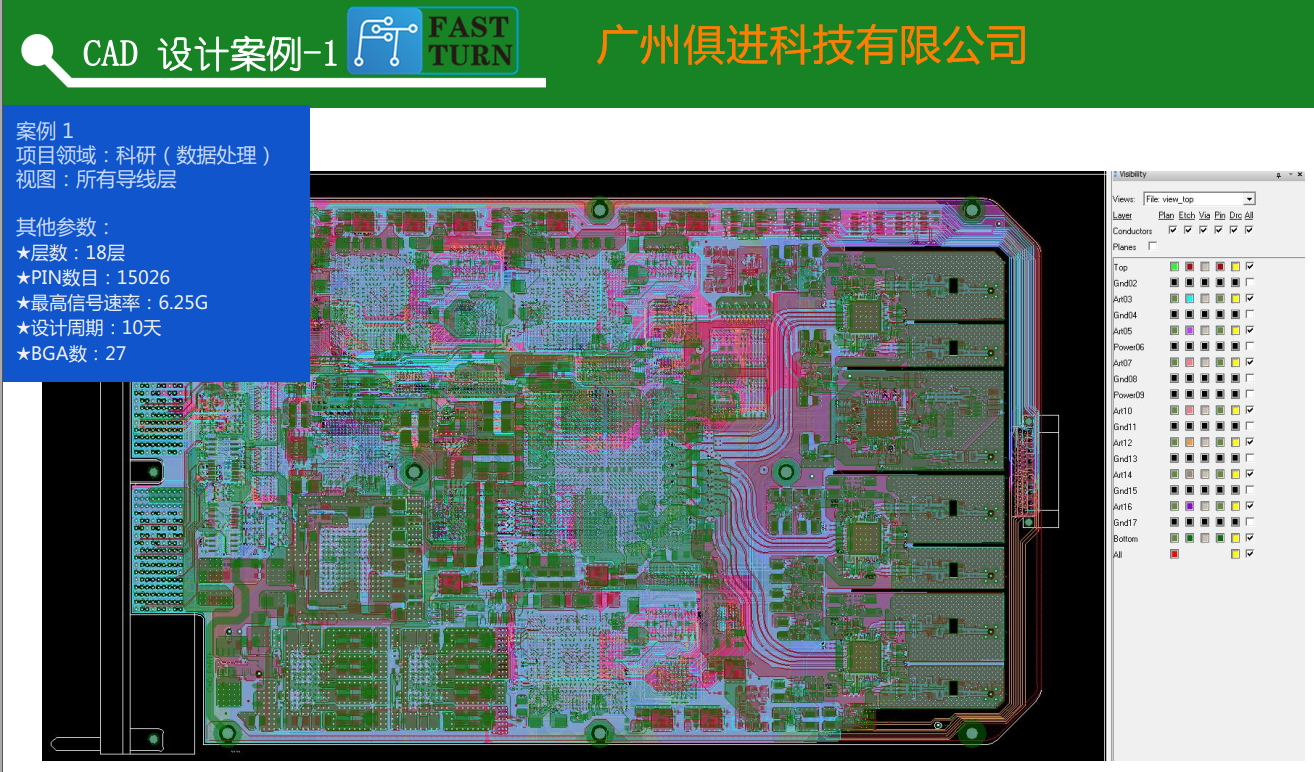

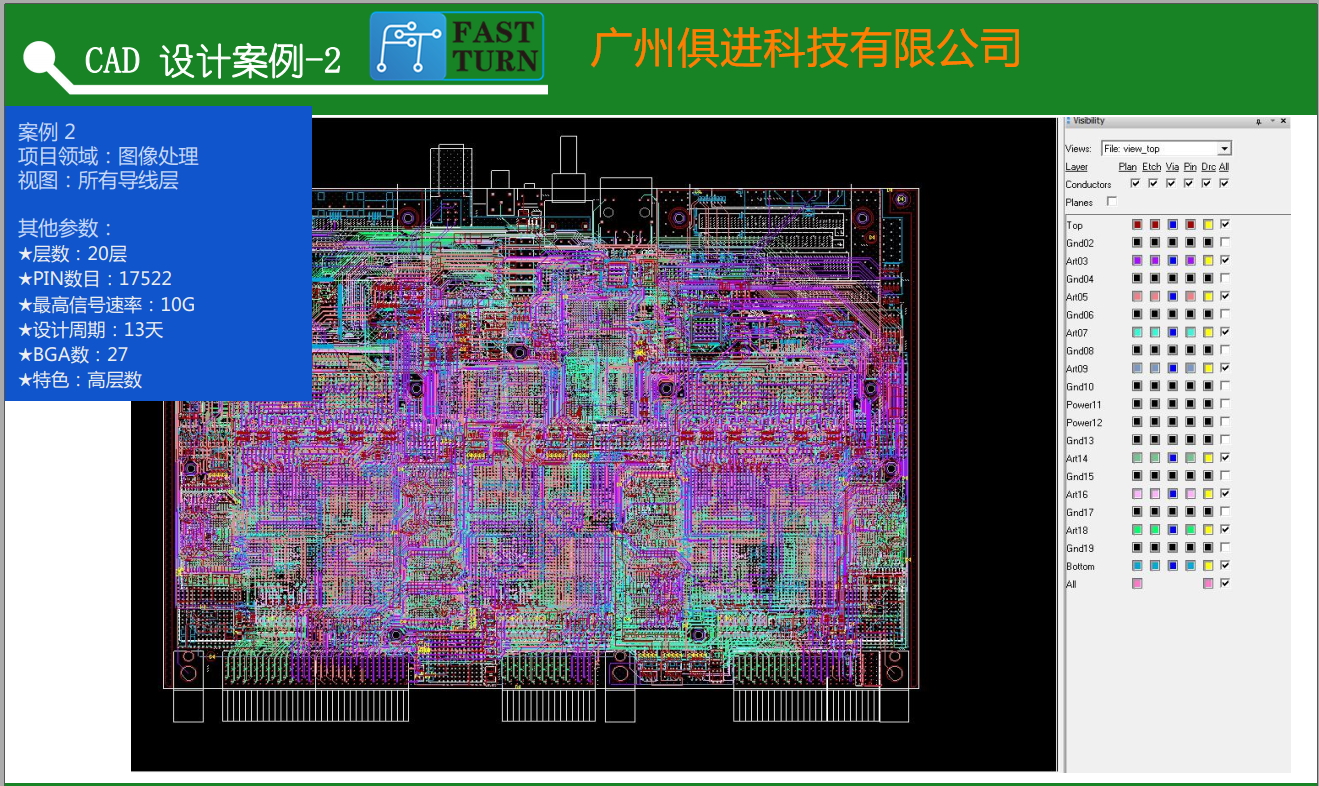

广州俱进科技:PCB存储模块设计小总结

-

科技滚动

正文

PCB设计的过程中,关注的是它们存取数据的速率,这个速率关系的细节的处理,PCB 设计时为了减小串扰,尽量拉大信号线的间距;下面广州俱进科技PCB设计工程师结合FLASH 、SDRAM 、DDR来介绍PCB布局布线设计要点。

PCB布局:内存中的数据是用来被控制器(CPU,如DSP 、MCU 、ARM 、FPGA 等)读写的,因此需要结合PCB 单板尺寸、器件密度、走线密度情况,预留后续做等长空间,选择合适的位置摆放。

PCB布线:首先要对信号线分类,然后分好组,处理这两步后,后续的扇孔、走线和绕等长等,同一组的按统一标准处理就行了。在这里将信号线分为三类:数据信号、地址信号、控制信号。对于PCB 设计工程师,首先要培养出在原理图中识别信号种类的能力,能够在PCB布线中能把分类的信号线进行分组。通俗的分组方法:数据组和地址组。

FLASH 设计

Flash 的速率一般比较低,因此在布局和布线方面放的比较宽松。Flash 的DQxx 为数据信号;Axx 为地址信号;Flash布局摆放时,尽量留足空间扇孔、扇线和绕等长;

Flash 布线注意一下三点:

a. Flash 信号线需要控制阻抗,阻抗为50Ω;

b. 如果空间允许,信号线间距为3W ;

c. 等长控制范围:10mil内;

SDRAM 设计

需要注意的是两个信号:DQML 和DQMH ,这两个信号是数据信号的掩码信号,分别属于低8位和高8位。因此在分组时,分别把它们添加到低8位组和高8位组。这样每个数据小组将有9根信号线。

SDRAM布局:尽量使信号线不要太长,靠近控制器放置;

对于1片SDRAM,采用“点对点”拓扑。

至于两片的拓扑,可以看下文DDR2设计的布局,布局要灵活,最好能举一反三。

SDRAM布线:

a.分组:根据前面介绍的数据分类,数据组可分为低8位和高8位两组:

低8位:(BUS名称可自定义一个有意义的名称):D0~D7、DQML,共9根信号线;

高8位:D8~D15、DQMH,共9根信号线;

注:有时候网络名称可能不这么命名,也要能够识别出来;

地址和控制信号分成一组;

b.信号线控制阻抗为50Ω,保持有完整的参考平面;

c.拉大信号线间距,保持3W间距;

d.等长控制:参照时钟等长;

e.等长误差控制范围:数据组:10mil;地址组:10mil;

f.在信号层换层的附近添加一些回流地过孔;

DDR设计

DDR可以看作是SDRAM的升级,相比较下,数据线分组分别出现了低8位锁存信号(LDQS)和高8位锁存信号( UDQS),此时每个小组有10根信号线了;而地址、控制、时钟仍为一组。

而DDR2是DDR的升级,数据交换速率升高了;同时在管脚方面也有一些变化:DDR 的单端信号锁存信号变成了一对差分信号,这样一来,数据小组每组有11根信号线。

另外一个变化就是工作电压的变化,通常FLASH为3.3V、SDRAM/DDR为2.5V,DDR2为1.8V,到后面的DDR3变为1.5V,因为较低的电压可以带来电平更快的翻转。

DDR2的布线

和SDRAM的要求类似;也有一些变化:

a.由于有了差分信号线,差分信号阻抗控制为100Ω;

b.差分需要做对内等长,误差控制在5mil;

c.等长误差控制范围要求更高:数据线:10mil;地址:10mil;

d.请注意VREF电源,这个走线要求加粗15~30mil;滤波电容靠近DDR管脚放置;

DDR2的布局

前面分别介绍了FLASH和SDRAM的布局,仅为1颗的情况下采用点对点的布局。在存在多颗时,布局也比较固定。(布局时,器件间距控制,布局者自己把握)2颗内存颗粒,有两种方式:关于控制器对称放置和顶底对贴放置。

地址信号的拓扑结构,我们通常称为远端分支,也叫做“T”型拓扑,地址信号先接到正中间,然后分到两边的DDR,正中间的VIA称之为T点;

当空间比较有限时候,采用顶底对贴的布局方式,地址部分依然可以采用上面“T”型拓扑扇孔方式,而数据部分的扇孔就比较麻烦了,需要手动调整。

当有4颗DDR时,布局思路同两颗类似:空间足够,放在同一面,此时注意T点的位置;空间比较有限时,先两两对贴,然后再采用T型拓扑;

还有一种拓扑形式:菊花链,通常在DDR3的布局中比较多的采用;还有一种菊花链的形式:控制器驱动多路负载,如CPU后挂的有SDRAM,同时夜游FLASH,这时候采用菊花链拓扑:CPU---SDRAM---FLASH,优先保证速率高的信号拓扑。

关于DDR布局,还有很多衍生的布局,如5颗DDR2,其中有一颗是纠错用的,通常放在中间,它的地址线在做等长时,不再和其他4颗放在一起了,其他4颗内存也能形成比较完美的T型拓扑。

以上信息是由广州俱进科技有限公司PCB设计工程师为您总结的几点PCB存储模块设计,希望对您所有帮助。

更多资讯请浏览:www.jujinpcb.com

---------------------------------------------------------

免责声明:

1.本文援引自互联网,旨在传递更多网络信息,仅代表作者本人观点,与本网站无关。

2.本文仅供读者参考,本网站未对该内容进行证实,对其原创性、真实性、完整性、及时性不作任何保证。

评论 {{userinfo.comments}}

-

{{child.nickname}}

{{child.create_time}}{{child.content}}

{{question.question}}

提交

苹果首款折叠屏iPhone曝光:仅售两款低调配色,定价或14999元起

微信状态访客记录冲上热搜!客服回应:仅iOS端灰度测试中

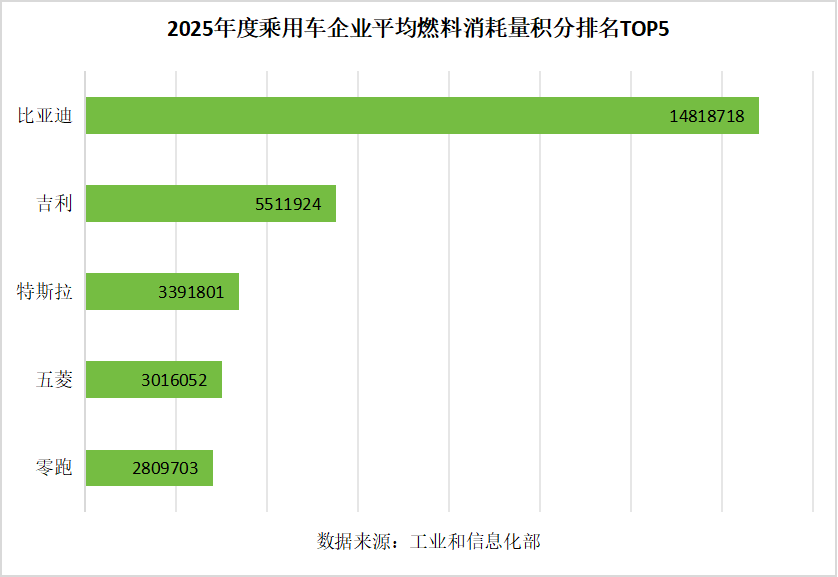

“智驾平权”落地,增配不加价!比亚迪2026款海鸥正式上市,售价6.99-9.79万元

告别“凑钱”烦恼!微信转账灰度测试“组合支付”新功能

驱动号 更多